# Experiment No. 3 Hazards and Glitches ECE 446

Peter Chinetti

September 16, 2014

Date Performed: September 9, 2014 Instructor: Professor Shanechi

#### 1 Introduction

A glitch is an unwanted transient pulse at the output of a combinational circuit, and a circuit with the potential for a glitch is said to have a hazard. Not all designs will produce glitches, however, if the timing of a circuit is of critical importance, the potential for glitches must be considered and their presence may be corrected.

#### 2 Procedure

- a. Generate minimized equations.

- b. Wire minimized circuit.

- c. Measure gate delay.

- d. Observe glitch.

- e. Add term to repair glitch.

- f. Observer working circuit.

### 3 Equipment

- Logic analyizer

- Breadboard

- Assorted gates

# 4 Results

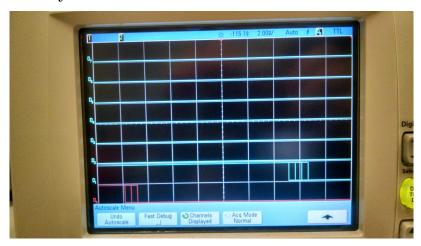

# 4.1 Delay

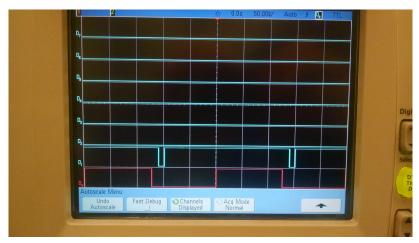

#### 4.2 Glitch

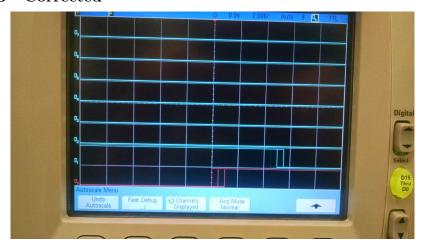

## 4.3 Corrected

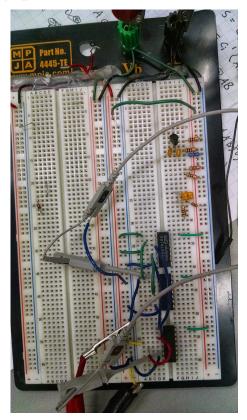

## 4.4 Breadboard

## 5 Conclusions

The purpose of this lab was achieved. A logic glitch was observed and corrected. In the future, logic will be designed to accomidate glitches.